TTL logika

Z důvodů uvedených v odstavci 1.5.1 se velmi často jak na amatérské úrovni, tak na profesionální úrovni používá spínání založené na TTL. Vzhledem k tomu, že je nutné pomocí integrovaných obvodů realizovat logické funkce, vyrábějí se:

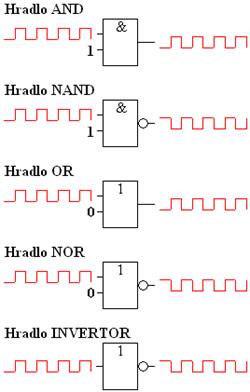

1. hradlo AND - realizuje logický součin ![]() ;

;

2. hradlo NAND - realizuje negaci logického součinu ![]() ;

;

3. hradlo OR - realizuje logický součet ![]() ;

;

4. hradlo NOR - realizuje negaci logického součtu ![]() ;

;

5. hradlo INVERTOR - realizuje negaci vstupní proměnné ![]() .

.

Schématické značky popsaných hradel a ukázky vybraných vstupů těchto hradel spolu s výstupy jsou zobrazeny na obr. 11.

|

| Obr. 11 |

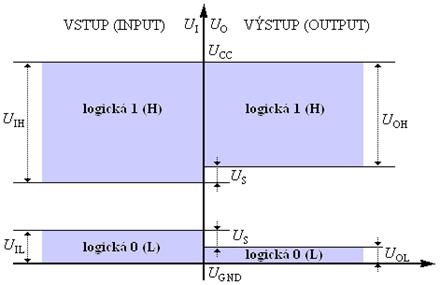

Každé z těchto hradel má vstup (input) a výstup (output). Hodnoty logických nul a logických jedniček jsou realizovány různým napětím přivedeným na vstup hradla. Podle hodnoty napětí na výstupu hradla pak pracuje další část obvodu: logické jedničce odpovídá jiný interval napětí než odpovídá logické nule. Na obr. 12 jsou hladiny napětí hradel schématicky zobrazeny. Označení odpovídá této legendě:

![]() je napětí na vstupu hradla;

je napětí na vstupu hradla;

![]() je napětí na výstupu hradla;

je napětí na výstupu hradla;

![]() je napětí zdroje, k němuž je hradlo připojeno, a jeho hodnota je +5 V;

je napětí zdroje, k němuž je hradlo připojeno, a jeho hodnota je +5 V;

![]() je napětí odpovídající logické jedničce na vstupu hradla, pro které platí

je napětí odpovídající logické jedničce na vstupu hradla, pro které platí ![]() ;

;

![]() je napětí odpovídající logické nule na vstupu hradla, pro které platí

je napětí odpovídající logické nule na vstupu hradla, pro které platí ![]() ;

;

![]() je napětí odpovídající logické jedničce na výstupu hradla, pro které platí

je napětí odpovídající logické jedničce na výstupu hradla, pro které platí ![]() ;

;

![]() je napětí odpovídající logické nule na výstupu hradla, pro které platí

je napětí odpovídající logické nule na výstupu hradla, pro které platí ![]() ;

;

![]() je napětí statické šumové imunity, jehož hodnota je 0,4 V (tj.

je napětí statické šumové imunity, jehož hodnota je 0,4 V (tj. ![]() resp.

resp. ![]() ). Toto napětí vyjadřuje, do jaké míry může být výstupní napětí ovlivněno různými šumy nebo parazitní elektromagnetickou indukcí v daném obvodu, aniž by ovlivnilo správnou činnost obvodu (tj. hlavně detekci stavu na vstupu do následujícího integrovaného obvodu).

). Toto napětí vyjadřuje, do jaké míry může být výstupní napětí ovlivněno různými šumy nebo parazitní elektromagnetickou indukcí v daném obvodu, aniž by ovlivnilo správnou činnost obvodu (tj. hlavně detekci stavu na vstupu do následujícího integrovaného obvodu).

Oblast napětí mezi 0,8 V a 2,0 V je zakázaná oblast, tzn. je nutné zabezpečit, aby napětí v daném obvodu nenabývalo hodnot z tohoto intervalu.

|

| Obr. 12 |

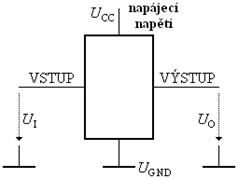

Každé z hradel má svá specifika (různé parametry, způsob zapojení, …). Obecně je činnost hradla velmi jednouchá: má jeden nebo více vstupů, jeden výstup, napájení a uzemnění (viz obr. 13).

|

| Obr. 13 |

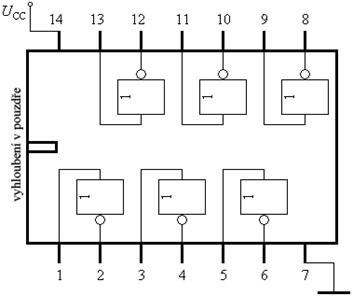

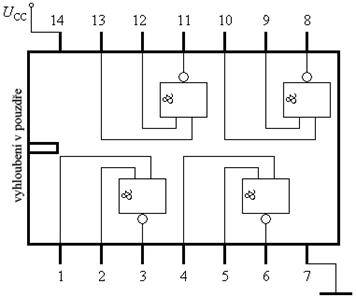

V praxi se pak většinou vyrábí z ekonomických důvodů i praktických důvodů více hradel téhož druhu v jednom pouzdře. Pouzdra mají normalizované značení a k dané součástce je nutné mít k dispozici schéma jejího zapojení. Na obr. 14 je zobrazena jedna z možností zapojení více hradel INVERTOR (TTL74LS04) a na obr. 15 jedna z možností zapojení více dvouvstupých hradel NAND (TTL74LS00). Obě součástky jsou zakresleny při pohledu shora.

|

| Obr. 14 |

|

| Obr. 15 |