Hradlo NAND

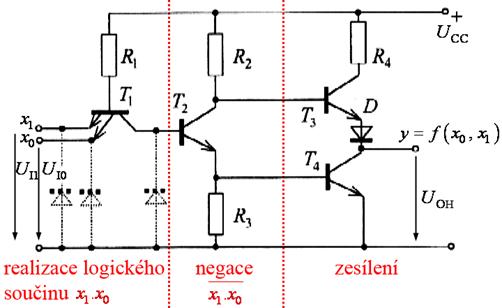

Vzhledem k jisté „unifikovanosti“ hradel se v praxi velmi často používá pouze jeden typ hradla s tím, že ostatní hradla lze pomocí jednoho vybraného hradla realizovat také. V praxi (zejména pro účely tohoto textu) se často používá jen hradlo NAND a INVERTOR. Zapojení integrované struktury logického obvodu hradla NAND se dvěma vstupy ![]() a

a ![]() a jedním výstupem y je zobrazeno na obr. 17.

a jedním výstupem y je zobrazeno na obr. 17.

|

| Obr. 17 |

Hodnoty odporů uvedených rezistorů jsou ![]() ,

, ![]() ,

, ![]() a

a ![]() .

.

Tranzistor ![]() rozděluje proud tekoucí jeho bází a rezistorem o odporu

rozděluje proud tekoucí jeho bází a rezistorem o odporu ![]() . Je-li alespoň jeden ze vstupů

. Je-li alespoň jeden ze vstupů ![]() a

a ![]() na úrovni logická nula (úroveň L - viz obr. 16), tj. je spojen se zemnícím vodičem, protéká zmíněný proud přes přechod báze - emitor tranzistoru

na úrovni logická nula (úroveň L - viz obr. 16), tj. je spojen se zemnícím vodičem, protéká zmíněný proud přes přechod báze - emitor tranzistoru ![]() (tento přechod je zapojen v propustném směru). Tranzistor

(tento přechod je zapojen v propustném směru). Tranzistor ![]() je tak saturován - tj. na jeho kolektoru je velmi malé napětí, a tranzistor

je tak saturován - tj. na jeho kolektoru je velmi malé napětí, a tranzistor ![]() je proto uzavřen. Jeho emitorový proud je velmi malý, a proto napětí na rezistoru s odporem

je proto uzavřen. Jeho emitorový proud je velmi malý, a proto napětí na rezistoru s odporem ![]() je také velmi malé. Tranzistor

je také velmi malé. Tranzistor ![]() je proto uzavřen. Proud procházející rezistorem o odporu

je proto uzavřen. Proud procházející rezistorem o odporu ![]() prochází i přes emitorový přechod tranzistoru

prochází i přes emitorový přechod tranzistoru ![]() a přes diodu D do zátěže připojené na výstup y. Tímto proudem se saturuje tranzistor

a přes diodu D do zátěže připojené na výstup y. Tímto proudem se saturuje tranzistor ![]() a proud procházející zátěží dosáhne hodnoty

a proud procházející zátěží dosáhne hodnoty ![]() . Napětí na zátěži dosáhne hodnoty

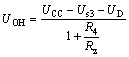

. Napětí na zátěži dosáhne hodnoty ![]() , pro kterou platí

, pro kterou platí

|

| (5) |

kde ![]() je saturační napětí tranzistoru

je saturační napětí tranzistoru ![]() (řádově 0,1 V) a

(řádově 0,1 V) a ![]() je napětí na diodě D (řádově 0,7 V). Přitom zanedbáme proud procházející bází tranzistoru

je napětí na diodě D (řádově 0,7 V). Přitom zanedbáme proud procházející bází tranzistoru ![]() .

.

Vzhledem k tomu, že

|

| (6) |

kde ![]() je odpor zátěže, je možné pro napětí

je odpor zátěže, je možné pro napětí ![]() definované vztahem (4) postupně psát:

definované vztahem (4) postupně psát: ![]() , odkud

, odkud ![]() . Dostáváme tedy

. Dostáváme tedy

. .

| (7) |

Pro hodnoty ![]() a

a ![]() je podle vztahu (6)

je podle vztahu (6) ![]() . Tato hodnota leží v oblasti, ve které detekujeme na výstupu hradla úroveň odpovídající logické jedničce.

. Tato hodnota leží v oblasti, ve které detekujeme na výstupu hradla úroveň odpovídající logické jedničce.

Na základě předpokládaných hodnot vstupních proměnných ![]() a

a ![]() jsme získali výsledek, který je ve shodě s činností hradla NAND.

jsme získali výsledek, který je ve shodě s činností hradla NAND.

Přivedeme-li na oba vstupy ![]() a

a ![]() napětí vyšší než 2 V (tj. budou ve stavu logická jednička), bázový proud tranzistoru

napětí vyšší než 2 V (tj. budou ve stavu logická jednička), bázový proud tranzistoru ![]() bude procházet přes kolektorový přechod na bázi tranzistoru

bude procházet přes kolektorový přechod na bázi tranzistoru ![]() a tranzistor

a tranzistor ![]() se proto otevře. Napětí na bázi tranzistoru

se proto otevře. Napětí na bázi tranzistoru ![]() dosáhne hodnoty, při níž se tranzistor

dosáhne hodnoty, při níž se tranzistor ![]() saturuje a napětí na jeho výstupu dosáhne hodnoty menší než 0,4 V. Napětí na kolektoru tranzistoru

saturuje a napětí na jeho výstupu dosáhne hodnoty menší než 0,4 V. Napětí na kolektoru tranzistoru ![]() nedosahuje hodnoty nutné k průchodu bázového proudu tranzistorem

nedosahuje hodnoty nutné k průchodu bázového proudu tranzistorem ![]() - proto je tranzistor

- proto je tranzistor ![]() uzavřen. Diodou D a tedy i zátěží připojenou k výstupu y hradla prochází nulový proud. Na výstupu hradla je tedy nízká úroveň napětí - výstup je ve stavu logické nuly.

uzavřen. Diodou D a tedy i zátěží připojenou k výstupu y hradla prochází nulový proud. Na výstupu hradla je tedy nízká úroveň napětí - výstup je ve stavu logické nuly.

Tento stav je ve shodě s hodnotami vstupních proměnných ![]() a

a ![]() a s očekávaným výstupem hradla NAND.

a s očekávaným výstupem hradla NAND.

Diody vyznačené ve schématu na obr. 17 tečkovaně chrání obvod při záporných vstupních napětích.

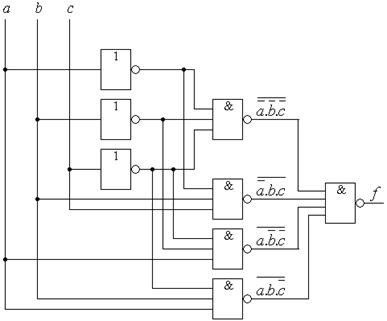

Pomocí hradel NAND je možné zapojit logické sítě libovolné logické funkce. Proto je nutné minimalizovanou logickou funkci přepsat ve tvaru, v němž se vyskytuje pouze negace součinu negovaných logických součinů. Do tohoto tvaru je možné součtový tvar zápis logické funkce upravit s využitím Booleovy algebry.

Pomocí dvouvstupého hradla NAND lze vytvořit i hradla vícevstupá, která se v praxi často používají.

|

| Obr. 18 |

Na základě tab. 6 byl vytvořen součtový tvar zápisu logické funkce f ve tvaru (4): ![]() . Ten lze přepsat tak, aby bylo možné tuto funkci realizovat pomocí hradel NAND:

. Ten lze přepsat tak, aby bylo možné tuto funkci realizovat pomocí hradel NAND: ![]() (byl použit zákon dvojité negace a následně de Morganův zákon). Logický obvod odpovídající této funkci bude vytvořen pomocí čtyř třívstupých hradel NAND, jednoho čtyřvstupého hradla NAND a pomocí tří hradel INVERTOR (viz obr. 18).

(byl použit zákon dvojité negace a následně de Morganův zákon). Logický obvod odpovídající této funkci bude vytvořen pomocí čtyř třívstupých hradel NAND, jednoho čtyřvstupého hradla NAND a pomocí tří hradel INVERTOR (viz obr. 18).

Zůstanou-li nějaké vstupy hradla nepoužité (tj. nejsou zapojeny), zapojí se tyto nepoužité vstupy na logickou jedničku (tj. připojí se ke kladné svorce zdroje napětí ![]() ) přes ochranný rezistor o odporu zhruba

) přes ochranný rezistor o odporu zhruba ![]() až

až ![]() . Realizujeme tak vztah Booleovy algebry

. Realizujeme tak vztah Booleovy algebry ![]() .

.

Tato situace může nastat tehdy, když potřebujeme pro určitou úlohu např. 5tivstupé hradlo NAND, které nemáme. Máme ale osmivstupé hradlo, které použijeme s tím, že tři nevyužité vstupy připojíme na logickou jedničku.